Review Article Received: 06/27/20

Journal of Renewable and New Energy jrenew.ir

Accepted: 11/10/20

# Technical and economical analysis of emerging technologies for production of low thickness solar cell silicon wafers

Arash Khakzadshahandashti<sup>1\*</sup>, Mohsen Pirmohammadi<sup>2</sup>

1- Research and technology department, Mapna group, Tehran, Iran

2- Research and technology department, Mapna group, Tehran, Iran.

\* P.O.B. 19395/6448, Tehran, Iran, khakzad\_a@mapnagroup.com

Received: 27 June 2020 Accepted: 10 November 2020

### Abstract

(cc) BY

Polycrystalline silicon wafers are produced by carbothermic reduction of silicon oxides in electric arc furnaces. Leader silicon wafer producer companies use emerging production technologies to reduce the production cost of silicon wafers. These efforts lead to reduce the production cost of silicon wafers by 66%. Emerging technologies for production of kerfless silicon wafers with the low thickness are studied in this paper. Using of these technologies in comparison with the conventional production methods lead to reduce the production cost remarkably. These emerging technologies improved the value chain of silicon wafers of solar cell panels. Conventional methods of silicon wafers manufacturing produce high amount of kerf. Wafers produced with these emerging methods have good technical specifications such as thickness, total thickness variation and mechanical properties. These are drivers of the future of this technology.

Keywords: low thickness silicon wafers, implant and cleave, stress liftoff, total thickness variation

## **1. INTRODUCTION**

Polycrystalline silicon wafers are produced by carbothermic reduction of silicon oxides in electric arc furnaces. The value chain of silicon wafers production consists of production of metallurgical grade silicon, refining of mg-Si and production of solar grade polysilicon and finally production of wafets. A lot of kerfs will be produced during the slicing of poly – silicon in conventional methods [1].

1366 Technologies Company has claimed that they can produce silicon wafers with one - third price of conventional methods. Today, the production price of silicon wafers is 0.29\$ per watt, but 1366 Technologies Company has reduced the price to 0.1\$ per watt. The method used by this company for production of wafers is called direct wafer method. In this method, silicon wafers will be produced from silicon melt directly [2-4].

# 2. Emerging technologies of silicon wafers production

Silicon wafers will be produced with high efficiency in kerf-less and direct methods. These methods are much cheaper compared to conventional methods with slicing of wafers. Production of these high technology wafers with standard dimensions leads to several progresses in the PV industry. Economical benefits, higher production rate and higher efficiency are the advantages of using these emerging technologies. Minimum amount of kerfs will be produced in kerfless method. In addition to 1366 Technologie Company, other companies such as SiGen, Twin Creeks, Solexel, Crystal Solar, Ampulse, Evergreen Solar, Solvio A.G., Varian, IMEC and Astrowatt has introduced different emerging technologies based on kerf-less methods. The difference of these technologies is in small details [5,6]. Two main methods are discussed in this paper. These methods are implant and cleave and stress liftoff method.

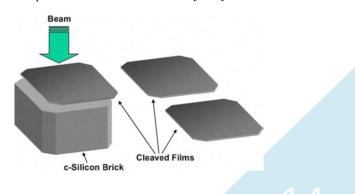

In implant and cleave method, a beam is radiated to a crystalline silicon, and wafers will be produced by cleavage of crystalline planes. Thin wafers with the thickness of 20 to 150 microns will be produced by using of this method [7]. Producing of wafers by using of this kerf-less method leads to economical benefits, and reduces the production price of silicon wafers by 60% (50 \$ per Kg). In addition mechanical properties tests showed better or equal values of tensile strength in compared to conventional methods [8-10].

Figure 1. Implant and cleave technology of crystalline silicon wafers production [7].

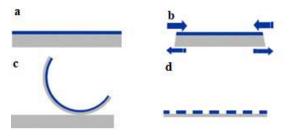

In stress liftoff method, a metallic layer is printed on a silicon block substrate. Then, the substrate and the metallic layer will be annealing heat treated. The difference between thermal expansions of silicon and metallic layer leads to residual thermal stresses. This stress leads to liftoff a thin silicon layer with the metallic layer with the thickness of 40 to 50 microns. Then, the metallic layer will be cleaned by an etch solution [11].

Figure 2. Schematic of silicon wafers production in stress liftoff method. a) metallic layer precipitation b) inducing thermal stresses c) liftoff the layer d) cleaning by the etch solution [11].

Other methods are also introduced for production of low thickness poly silicon wafers. The purpose of these methods is producing of kerf less silicon wafers without cutting. One of these methods is chemical vapor deposition (CVD). In this method, a thin precipitated silicon layer is produced by accurate controlling of process parameters. This method has high potential for mass production, and doesn't need very high setup cost. It is noteworthy to say that the controlling of high temperature in CVD method is very challenging, and this method is very energy intensive [12].

String ribbon is another method considered for production of kerf-less silicon wafers. Challenges of this method are low production rate and high setup cost [13]. According to aforementioned explanations, table 1 shows the comparison of mentioned methods in different aspects.

| Table 1. Methods | comparison of low | thickness silicon |

|------------------|-------------------|-------------------|

|                  | production        |                   |

| Method         | Phase  | Silicon<br>source | Mass<br>production<br>capability |

|----------------|--------|-------------------|----------------------------------|

| Implant and    | solid  | Crystalline       | high                             |

| cleave         |        | silicon           | e                                |

| Stress liftoff | solid  | Silicon           | medium                           |

|                |        | substrate         |                                  |

| CVD            | vapor  | CVD               | low                              |

|                |        | reactor           |                                  |

| String ribbon  | liquid | Silicon           | medium                           |

|                |        | melt              |                                  |

# 3. Conclusions

Technical aspects of low thickness silicon wafers production is presented in this paper. Emerging silicon wafers are compared technically and economically with conventional methods. Emerging technologies have the ability to produce silicon wafers of 20 to 150 microns without kerf, and similar properties in compared to conventional methods. These are the divers of adoption of mentioned emerging technologies in near future.

## 4. References

- Xakalashe, B.S. and Tangstad, M., Silicon processing: from quartz to crystalline silicon solar cells, *Chem Technol*, (March), pp.6-9, 2012.

- [2] Van Mierlo, F., Jonczyk, R. and Qian V., Next generation Direct Wafer® technology delivers low cost, high performance to silicon wafer industry. *Energy Procedia*, Vol. 130, pp.2-6, 2017.

- [3] T Lorenz, A., Kerfless Silicon Precursor Wafer Formed by Rapid Solidification, October 2009-March 2010 (No. NREL/SR-5200-51934). National Renewable Energy Lab. (NREL), Golden, CO (United States), 2011.

- [4] Montgomery, J., 1366 Technologies Opens New Factory Paves Road to Cheaper Solar PV, RenewableEnergyWorld, 1, 2013.

- [5] Brailove, A., Kang, S., Fujisaka, A. and Henley, F., First demonstration of high volume manufacturing of kerf-free polymax wafers. In *Proc. of the 25th European Photovoltaic Solar Energy Conf* (p. 1613), 2010.

- Fujisaka, A., Keeping Pace with Cost Reduction as Module Prices Continue to Decline. *Photovoltaics World*, pp.38-41, 2010.

- [7] Henley, F., Kang, S., Liu, Z., Tian, L., Wang, J. and Chow, Y.L., June. Beam-induced wafering technology for kerf-free thin PV manufacturing. In 2009 34th IEEE Photovoltaic Specialists Conference (PVSC) (pp. 001718-001723). IEEE, 2009.

- [8] Fujisaka, A., Kang, S., Tian, L., Chow, Y.L. and Belyaev, A., Implant-cleave process enables ultra-thin wafers without kerf loss. *Photovoltaics World*, pp.21-24.

- [9] Standard, A.S.T.M., Standard test method for monotonic equibiaxial flexural strength of advanced ceramics at ambient temperature. *Standard ASTM C1499-04, West Conshohocken*, 2005.

- [10] Coletti, G., Van Der Borg, N.J.C.M., De Iuliis, S., Tool, C.J.J. and Geerligs, L.J., Mechanical strength of silicon wafers depending on wafer thickness and surface treatment, Vol. 2000, No.80, p.86, 2006.

- [11] Dross, F., Milhe, A., Robbelein, J., Gordon, I., Bouchard, P.O., Beaucarne, G. and Poortmans, J., May. Stress-induced lift-off method for kerf-loss-free wafering of ultra-thin (~ 50 μm) crystalline Si wafers. In 2008 33rd IEEE Photovoltaic Specialists Conference (pp. 1-5). IEEE, 2008.

- [12] Li, N., Habuka, H., Ikeda, S.I. and Hara, S., Silicon chemical vapor deposition process using a half-inch silicon wafer for Minimal Manufacturing System. *Physics Procedia*, Vol. 46, pp.230-238, 2013.

- [13] Nakayashiki, K., Rousaville, B., Yelundur, V., Kim, D.S., Rohatgi, A., Clark-Phelps, R. and Hanoka, J.I., Fabrication and analysis of high-efficiency String Ribbon Si solar cells. *Solid-state electronics*, Vol 50, pp. 1406-1412, 2006.